Meta's AI-chip lavet med TSMC's 5nm proces

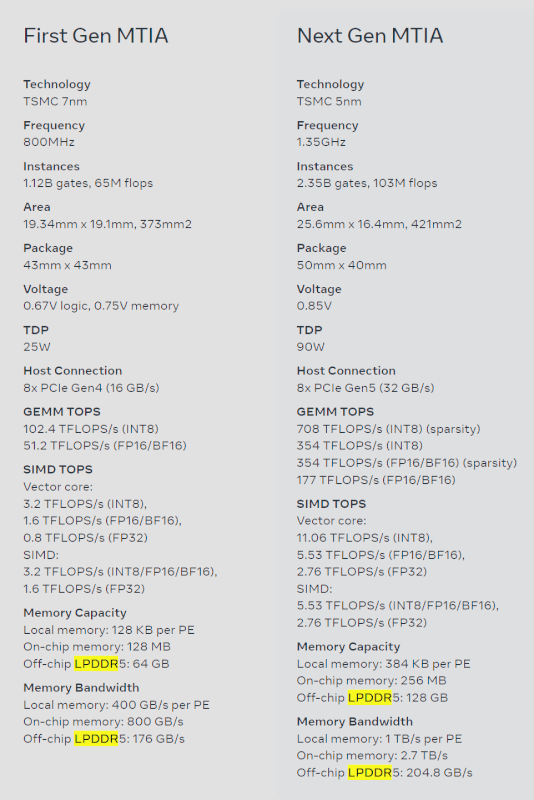

Meta har netop givet os et smugkig på deres næste generations AI-chip - MTIA, der er en opgradering over deres nuværende chip, MTIA v1. Den nye MTIA-chip er produceret på TSMC's nyere 5nm procesnode, hvor den originale MTIA-chip blev produceret på 7nm.

Den nye Meta Training and Inference Accelerator (MTIA) chip er "fundamentalt fokuseret på at levere den rette balance mellem beregning, hukommelsesbåndbredde og hukommelseskapacitet" der vil blive brugt til Metas unikke behov. Vi har set de bedste AI-GPU'er i verden bruge HBM-hukommelse, med HBM3 brugt på NVIDIAs Hopper H100 og AMD Instinct MI300 serie AI-chips, men Meta bruger i stedet lav-effekt DRAM-hukommelse (LPDDR5) i stedet for server DRAM eller LPDDR5-hukommelse.

Det sociale netværksgigant skabte sin MTIA chip som et førstegenerations AI inference accelerator, der blev designet internt til Meta's AI arbejdsbyrde. Virksomheden siger, at deres deep learning anbefalingsmodeller "forbedrer en række oplevelser på tværs af vores produkter".

Metas langsigtede mål og deres rejse med AI inference processoren er at levere den mest effektive arkitektur til Metas unikke arbejdsbyrder. Virksomheden tilføjer, at da AI arbejdsbyrder bliver stadig vigtigere for Metas produkter og tjenester, vil effektiviteten af deres MTIA chips forbedre deres evne til at levere de bedste oplevelser for deres brugere over hele kloden.

Meta forklarer på deres hjemmeside for MTIA: "Denne chips arkitektur er fundamentalt fokuseret på at levere den rette balance mellem beregning, hukommelsesbåndbredde og hukommelseskapacitet til betjening af rangerings- og anbefalingsmodeller. I inference skal vi være i stand til at levere relativt høj udnyttelse, selv når vores batch-størrelser er relativt lave. Ved at fokusere på at levere outsized SRAM kapacitet, i forhold til typiske GPU'er, kan vi levere høj udnyttelse i tilfælde, hvor batch-størrelser er begrænsede, og levere tilstrækkelig beregning, når vi har større mængder potentielt samtidigt arbejde.

Denne accelerator består af en 8x8 gitter af processing elementer (PE). Disse PE'er leverer betydelig forbedret tæt beregningsydelse (3,5x over MTIA v1) og sparsom beregningsydelse (7 gange forbedring). Dette kommer delvist fra forbedringer i arkitekturen forbundet med pipelining af sparsom beregning. Det kommer også fra, hvordan vi fodrer PE-gitteret: Vi har tredoblet størrelsen på det lokale PE-lager, fordoblet størrelsen på on-chip SRAM og øget båndbredden med 3,5X, og fordoblet kapaciteten af LPDDR5.

Seneste processor

-

29 aprprocessor

-

28 aprprocessor

Intel stadig i problemer

-

26 aprprocessor

Nye AMD Strix Point, Strix Halo spec leaks

-

26 aprprocessor

TSMC's nye COUPE tech klar i 2026

-

26 aprprocessor

Første NVIDIA DGX H200 til OpenAI

-

25 aprprocessor

Qualcomm afslører Snapdragon X Elite

-

25 aprprocessor

TSMC's 'A16' chip klar til at udfordre Intel i 202

-

25 aprprocessor

Nvidia er stadig stærke på AI men kan udfordres