AMD patenterer nyt chiplet GPU-design

AMD har offentliggjort sit første patent på et chiplet GPU-design. Chiplet-GPU'er er først lige begyndt at få fodfæste, og Intel har været ret informative om deres udviklingsproces og bekræftet integrationen af chiplets i deres første generations diskrete GPU'er. NVIDIA er at finde lidt i samme boldgade med hensyn til at spille med åbne kort, og har løbende offentliggjort adskillige forskningsartikler om emnet.

Nu melder AMD sig altså også ind i kampen.

Chiplets er, som navnet antyder, mindre og langt mindre komplekse chips, som er udviklet med henblik på at arbejde sammen i mere kraftfulde processorer. De er uden tvivl den uundgåelige fremtid for alle højtydende komponenter.

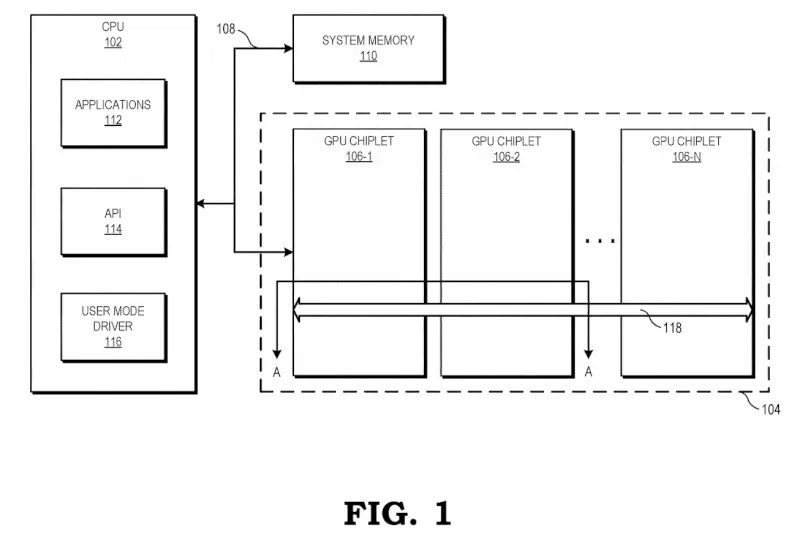

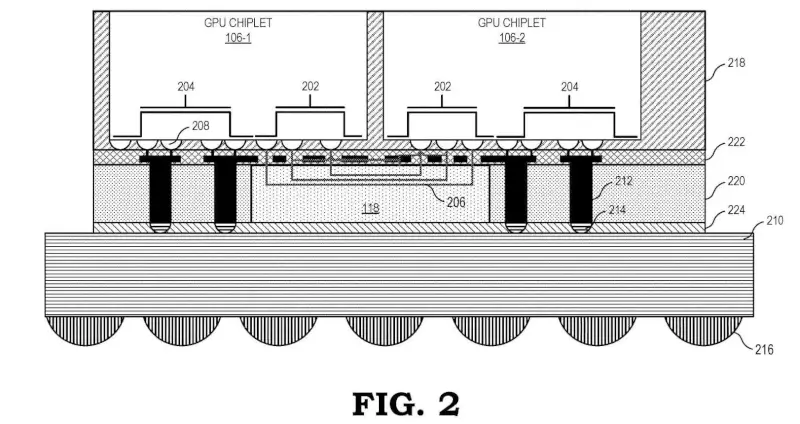

I det nye patent dateret 31. december skitserer AMD et chiplet-design, der er designet til at efterligne et monolitisk design så meget som muligt. Deres hypotetiske model bruger to chiplets forbundet med en højhastigheds inaktiv interposer også navngivet crosslink.

Et crosslink sidder mellem L2-cachen og L3-cachen i hukommelseshierarkiet. Alt under det, såsom kernerne og L1-cachen og L2-cachen, er opmærksomme på deres adskillelse fra den anden chiplet. Alt ovenfor, inklusive L3-cache og GDDR-hukommelse, deles mellem chiplets.

Dette design er fordelagtigt, netop fordi det er konventionelt og en konventionel tankegang inden for netop hardwarens verden.

AMD hævder, at computerenheder har adgang til lavt niveau cache på andre chiplets næsten lige så hurtigt som de kan få adgang til lokal lavt cache niveau. Hvis det viser sig at være sandt, behøver software ikke at blive opdateret som vi kender det i dagens teknologi.

Det samme kan ikke siges om Intel og NVIDIAs design. Intel har til hensigt at bruge to nye teknologier, EMIB (integreret multi-die interconnect bridge) og Foveros. Sidstnævnte er en aktiv interposer, der bruger gennem-silicium-vias, noget AMD udtrykkeligt siger, at de ikke vil bruge. Intels design lader GPU’en huse en system tilgængelig cache, der driver et nyt hukommelsesmodel.

NVIDIA har endnu ikke afsløret alt, men har angivet et par retninger, de kan følge. Et forskningsoplæg fra 2017 beskriver et fire-chiplet design og en NUMA (ikke-ensartet hukommelsesadgang) og en nye form for arkitektur. De eksperimenterer også med en ny L1.5-cache, som udelukkende opretholder fjernadgang til data og omgåes under lokal hukommelsesadgang.

Nedenfor er yderligere diagrammer fra patentet.

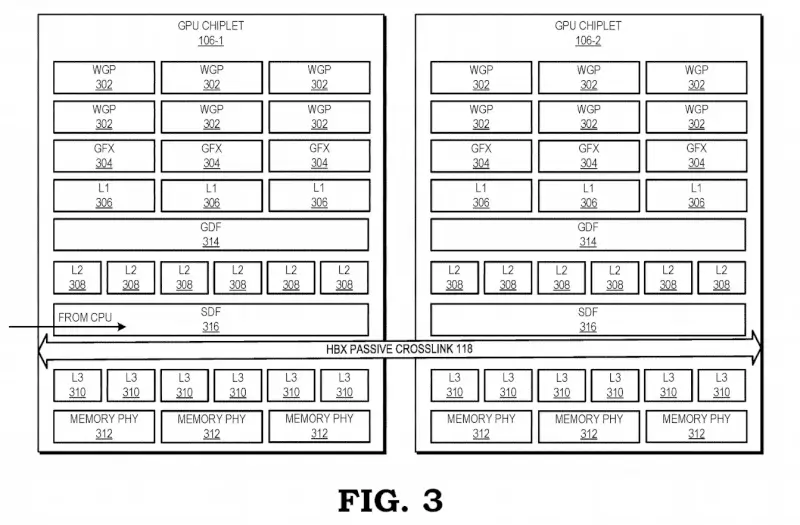

Figur 3 viser cachehierarkiet. WGP'er (arbejdsgruppeprocessorer) (302), som er samlinger af skyggekerner, og GFX'er (faste funktionsenheder) (304), som er dedikerede processorer til entydige formål, forbinder direkte til en kanals L1-cache (306). Hver chiplet indeholder flere L2-cache (308) bankes, der kan adresseres individuelt og også sammenhængende inden for en enkelt chiplet. Hver chiplet indeholder også flere L3-cache (310) cache-banks, der er sammenhængende på tværs af hele GPU'en.

GDF (graphics data fabric) (314) forbinder L1-cache-banks til L2-cache-banks. SDF (scalable data fabric) (316) kombinerer L2-cache-banks og forbinder dem til crosslinket (118). Crosslinket forbinder til SDF'erne på alle chiplets samt L3-cache-bankd på alle chiplets. GDDR-hukommelsesbanerne (skrevet som Memory PHY) (312) forbinder til L3-cache-banks.

Som et eksempel, hvis en WGP på en chiplet krævede data fra en GDDR-bank på en anden chiplet, ville disse data blive sendt igennem til en L3-cache-bank, derefter over crosslink til en SDF, derefter til en L2-bank og endelig gennem en GDF til en L1-bank.

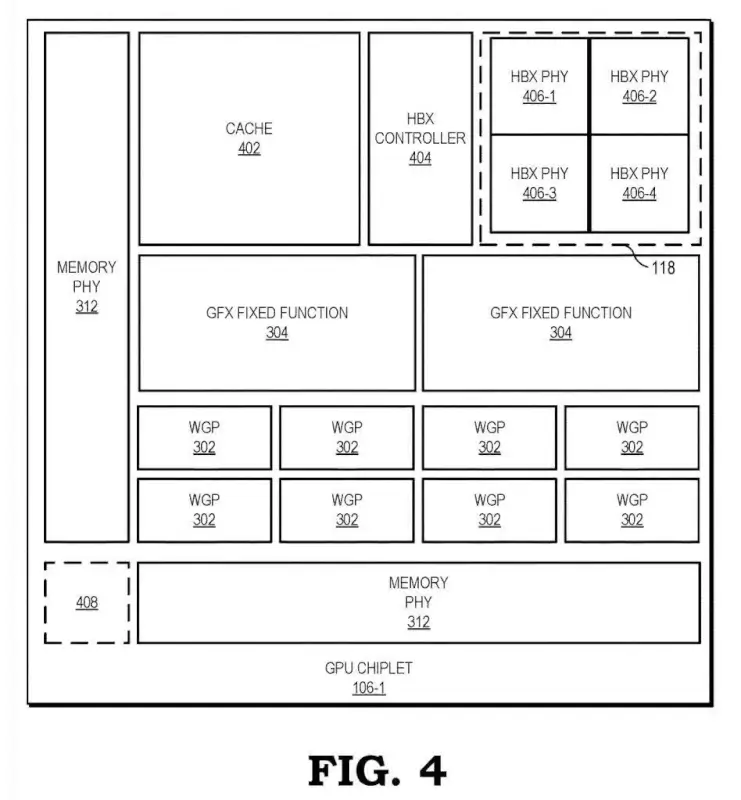

Figur 4 er et fugleperspektiv af en chiplet. Det viser mere nøjagtigt de potentielle placeringer og skalaer for forskellige komponenter. HBX-controlleren (404) styrer crosslinket, som chiplet er forbundet med HBX PHY (406) ledere. Den lille firkant i nederste venstre hjørne (408) er en potentiel yderligere forbindelse til crosslinket for at forbinde flere chiplets.

Seneste teknologi

-

-

05 julsmartphone

Nye OnePlus produkter lige om hjørnet

-

04 julsmartphone

Apple udfordrer Kinas antitrust-app afgørelse

-

04 julteknologi

AI-forventning øger Samsungs Q2 overskud

-

04 julteknologi

Alle er blevet ´utilgængelige` i det åbne kontor

-

Pixel 10 med Google's Tensor G5 chip, 3nm

-

03 julteknologi

Googles AI øger forurening

-

03 julsmartphone

Apple-brugere vinder ved Google Gemini AI-samarbej